# SPT9712

# 12-BIT, 100 MWPS ECL D/A CONVERTER

## **TECHNICAL DATA**

FEBRUARY 15, 2001

#### **FEATURES**

- 12-Bit, 100 MWPS digital-to-analog converter

- ECL compatibility

- Low power: 600 mW

- 1/2 LSB DNL

- 40 MHz multiplying bandwidth

- · Industrial temperature range

- Superior performance over AD9712

- Improved settling time of 13 ns

- Improved glitch energy 15 pV-s

- Master-slave latches

#### **APPLICATIONS**

- · Fast frequency hopping spread spectrum radios

- Direct sequence spread spectrum radios

- · Microwave and satellite modems

- Test & measurement instrumentation

#### **GENERAL DESCRIPTION**

The SPT9712 is a 12-bit, 100 MWPS digital-to-analog converter designed for direct digital synthesis, high resolution imaging, and arbitrary waveform generation applications.

This device is pin-for-pin compatible with the AD9712 with significantly improved performance. The only difference between the SPT9712 and the AD9712 is that the Latch Enable (LE, pin 26) for the SPT9712 is rising-edge trig-

gered (see figure 1), whereas the Latch Enable (LE, pin 26) for the AD9712 functions in the transparent mode.

The SPT9712 is an ECL-compatible device. It features a fast settling time of 13 ns and low glitch impulse energy of 15 pV-s, which results in excellent spurious-free dynamic range characteristics.

The SPT9712 is available in a 28-lead PLCC package in the industrial temperature range (-40 to +85 °C).

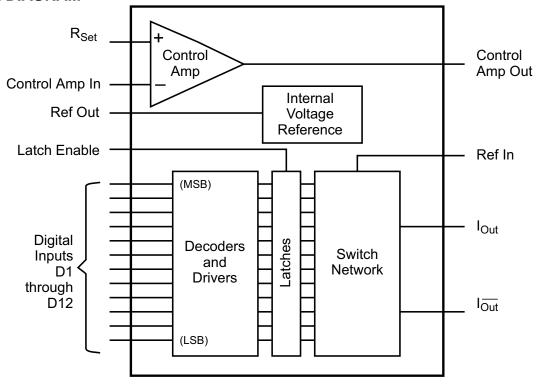

#### **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

#

| Output  | t Currents | 3 |     |

|---------|------------|---|-----|

| 1.040.0 | aal Dafara |   | 4 ( |

| Internal Reference Output Current | 500 µA  |

|-----------------------------------|---------|

| Control Amplifier Output Current  | ±2.5 mA |

## **Temperature**

| Operating Temperature        | 40 to +85 °C   |

|------------------------------|----------------|

| Junction Temperature         | +150 °C        |

| Lead, Soldering (10 seconds) | +300 °C        |

| Storage                      | –65 to +150 °C |

**Note:** 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied conditions in typical applications.

#### **ELECTRICAL SPECIFICATIONS**

$T_A = T_{MIN} - T_{MAX}$ ,  $V_{EE} = -5.2$  V,  $R_{Set} = 7.5$  k $\Omega$ , Control Amp In = Ref Out,  $V_{OUT} = 0$  V, unless otherwise specified.

|                                                                                                                                                                                                                                                                                                                                             | TEST                                                                                                                                                                | TEST SPT9          |             |                                                        | PT9712A                                                            |             | SPT9712B                                              |                                                                   |                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--------------------------------------------------------|--------------------------------------------------------------------|-------------|-------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                                                                                                  | CONDITIONS                                                                                                                                                          | LEVEL              | MIN         | TYP                                                    | MAX                                                                | MIN         | TYP                                                   | MAX                                                               | UNITS                                                                               |

| Resolution Differential Linearity Differential Linearity Integral Linearity Integral Linearity Integral Linearity Output Capacitance Gain Error Gain Error Tempco Zero-Scale Offset Error Offset Drift Coefficient Output Compliance Voltage Equivalent Output Resistance                                                                   | Max at Full Temp. Best Fit Max at Full Temp. +25 °C +25 °C Full Temp. Full Temp. +25 °C Full Temp. Full Temp. Full Temp. Full Temp. +25 °C Full Temp. +25 °C +25 °C |                    | -1.2<br>0.8 | 12<br>±0.5<br>±0.75<br>10<br>1.0<br>150<br>0.5<br>0.01 | ±0.75<br>±1.5<br>±1.0<br>±1.75<br>5.0<br>8.0<br>2.5<br>5.0<br>+2.0 | -1.2<br>0.8 | 12<br>±1.0<br>±1.0<br>10<br>1.0<br>150<br>0.5<br>0.01 | ±1.25<br>±2.0<br>±1.5<br>±2.0<br>5.0<br>8.0<br>2.5<br>5.0<br>+2.0 | Bits<br>LSB<br>LSB<br>LSB<br>pF<br>% FS<br>% FS<br>PPM/°C<br>μA<br>μA/°C<br>V<br>kΩ |

| Dynamic Performance Conversion Rate Settling Time t <sub>ST</sub> <sup>2</sup> Output Propagation Delay t <sub>D</sub> <sup>3</sup> Glitch Energy <sup>4</sup> Full Scale Output Current <sup>5</sup> Spurious-Free Dynamic Range <sup>6</sup> 1.23 MHz; 10 MWPS 5.055 MHz; 20 MWPS 10.1 MHz; 50 MWPS 16 MHz; 40 MWPS Rise Time / Fall Time | +25 °C<br>+25 °C<br>+25 °C<br>+25 °C<br>+25 °C<br>+25 °C<br>2 MHz Span<br>2 MHz Span<br>2 MHz Span<br>10 MHz Span<br>R <sub>L</sub> = 50 Ω                          | IV                 | 100         | 13<br>1<br>15<br>20.48<br>70<br>68<br>68<br>68<br>2    |                                                                    | 100         | 13<br>1<br>15<br>20.48<br>70<br>68<br>68<br>68<br>2   |                                                                   | MWPS ns ns pV-s mA  dBc dBc dBc dBc dBc ns                                          |

| Power Supply Requirements Negative Supply Voltage Negative Supply Current (-5.2 V) Nominal Power Dissipation Power Supply Rejection Ratio                                                                                                                                                                                                   | +25 °C<br>Full Temp<br>±5% of V <sub>EE</sub><br>External Ref, +25 °C                                                                                               | IV<br>I<br>VI<br>V | -5.46       | -5.2<br>115<br>600<br>30                               | -4.94<br>140<br>148<br>100                                         | -5.46       | -5.2<br>115<br>600<br>30                              | -4.94<br>140<br>148<br>100                                        | V<br>mA<br>mA<br>mW<br>µA/V                                                         |

<sup>1</sup>Gain is measured as a ratio of the full-scale current to I<sub>Set</sub>. The ratio is nominally 128.

SPT9712

<sup>&</sup>lt;sup>2</sup>Measured as voltage at mid-scale transition to  $\pm 0.024\%$ ; R<sub>L</sub>=50  $\Omega$ .

<sup>3</sup>Measured from the rising edge of Latch Enable to where the output signal has left a 1 LSB error band.

<sup>4</sup>Glitch is measured as the largest single transient.

<sup>&</sup>lt;sup>5</sup>Calculated using I<sub>FS</sub> = 128 x (Control Amp In / R<sub>Set</sub>)

<sup>6</sup>SFDR is defined as the difference in signal energy between the fundamental and worst case spurious frequencies in the output spectrum window, which is centered at the fundamental frequency and covers the indicated span.

## **ELECTRICAL SPECIFICATIONS**

$T_{A} = T_{MIN} - T_{MAX}, \ V_{EE} = -5.2 \ V, \ R_{SET} = 7.5 \ k\Omega, \ Control \ Amp \ In = Ref \ Out, \ V_{OUT} = 0 \ V, \ unless \ otherwise \ specified.$

| PARAMETERS                                                                                                                                                                                                                                                                     | TEST<br>CONDITIONS                                                                                       | TEST<br>LEVEL                         | MIN S                                 | PT9712<br>TYP                      | PA<br>MAX        | S<br>MIN                              | PT9712<br>TYP                      | 2B<br>MAX        | UNITS                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|------------------------------------|------------------|---------------------------------------|------------------------------------|------------------|--------------------------------------------------|

| Voltage Input and Control Reference Input Impedance Ref. Multiplying Bandwidth Internal Reference Voltage Internal Reference Voltage Drift Amplifier Input Impedance Amplifier Input Bandwidth                                                                                 | +25 °C<br>+25 °C<br>+25 °C<br>+25 °C                                                                     | V<br>V<br>VI<br>V<br>V                | -1.15                                 | 3<br>40<br>-1.20<br>50<br>3<br>1   | -1.25            | -1.15                                 | 3<br>40<br>-1.20<br>50<br>3<br>1   | -1.25            | kΩ<br>MHz<br>V<br>ppm/°C<br>MΩ<br>MHz            |

| Digital Inputs  Logic 1 Voltage  Logic 0 Voltage  Logic 1 Current  Logic 0 Current  Input Capacitance  Input Setup Time – ts  Input Setup Time – ts  Input Hold Time – t <sub>H</sub> Input Hold Time – t <sub>H</sub> Latch Pulse Width – t <sub>PWL</sub> , t <sub>PWH</sub> | Full Temp. Full Temp. Full Temp. Full Temp. +25 °C +25 °C Full Temp. +25 °C Full Temp. +25 °C Full Temp. | VI<br>VI<br>VI<br>V<br>IV<br>IV<br>IV | -1.0<br>3<br>3.5<br>0.5<br>0.5<br>5.0 | -0.8<br>-1.7<br>3<br>2<br>0<br>4.0 | -1.5<br>20<br>10 | -1.0<br>3<br>3.5<br>0.5<br>0.5<br>5.0 | -0.8<br>-1.7<br>3<br>2<br>0<br>4.0 | -1.5<br>20<br>10 | V<br>V<br>µA<br>µA<br>pF<br>ns<br>ns<br>ns<br>ns |

#### **TEST LEVEL CODES**

All electrical characteristics are subject to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data column indicates that the specification is not tested at the specified condition.

#### LEVEL TEST PROCEDURE

100% production tested at the specified temperature.

II 100% production tested at  $T_A$  = +25 °C, and sample tested at the specified temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characterization data.

V Parameter is a typical value for information purposes only.

VI 100% production tested at  $T_A = +25$  °C. Parameter is guaranteed over specified temperature range.

3

#### THEORY OF OPERATION

The SPT9712 uses a segmented architecture incorporating most significant bit (MSB) decoding. The four MSBs (D1–D4) are decoded to thermometer code lines to drive 15 discrete current sinks. For the eight least significant bits (LSBs), D5 and D6 are binary weighted and D7–D12 are applied to the R-2R network. The 12-bit decoded data is input to internal master/slave latches. The latched data is input to the switching network and is presented on the output pins as complementary current outputs.

#### TYPICAL INTERFACE CIRCUIT

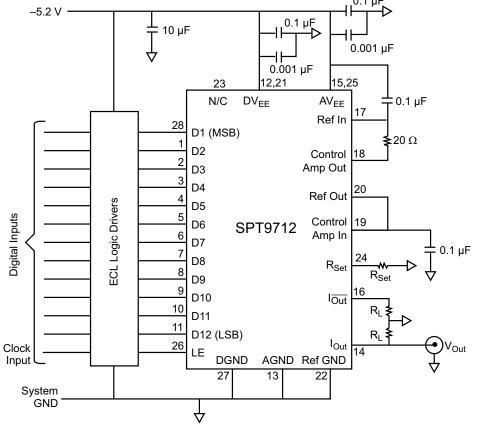

The SPT9712 requires few external components to achieve the stated operation and performance. Figure 2 shows the typical interface requirements when using the SPT9712 in normal circuit operation. The following sections provide descriptions of the pin functions and outline critical performance criteria to consider for achieving optimal device performance.

#### POWER SUPPLIES AND GROUNDING

The SPT9712 requires the use of a single -5.2 V supply. All supplies should be treated as analog supply sources. This means the ground returns of the device should be connected to the analog ground plane. All supply pins should be bypassed with .01  $\mu$ F and 10  $\mu$ F decoupling capacitors as close to the device as possible.

The two grounds available on the SPT9712 are DGND and AGND. These grounds are not tied together internal to the device. The use of ground planes is recommended to achieve the best performance of the SPT9712. All ground, reference and analog output pins should be tied directly to the DAC ground plane. The DAC and system ground planes should be separate from each other and only connected at a single point through a ferrite bead to reduce ground noise pickup.

#### **DIGITAL INPUTS AND TIMING**

The SPT9712 uses single-ended, 10K ECL-compatible inputs for data inputs D1–D12 and Latch Enable. It also employs master/slave latches to simplify digital interface timing requirements and reduce glitch energy by synchronizing the current switches. This is an improvement over the AD9712, which typically requires external latches for digital input synchronization.

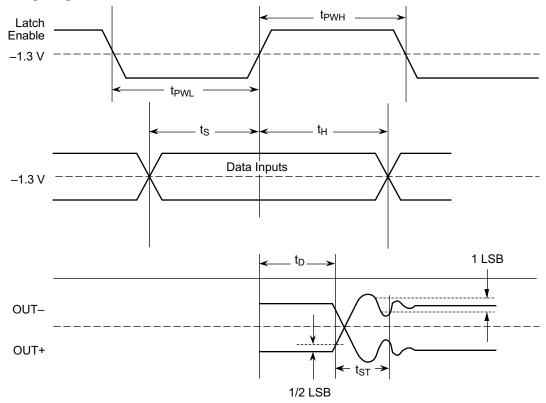

Referring to figure 1, data is latched into the DAC on the rising edge of the latch enable clock with the associated setup and hold times. The output transition occurs after a typical 1 ns propagation delay and settles to within ±1 LSB in typically 13 ns. Because of the SPT9712's rising-edge triggering, no timing changes are required when replacing an AD9712 operating in the transparent mode.

#### VOLTAGE REFERENCE

When using the internal reference, Ref Out should be connected to Control Amp In and decoupled with a 0.1  $\mu$ F capacitor. Control Amp Out should be connected to Ref In and decoupled to the analog supply. (See figure 2.)

Full-scale output current is determined by Control Amp In and R<sub>Set</sub> using the following formula:

$I_{Out}$  (FS) = (Control Amp In / R<sub>Set</sub>) x 128 (Current Out is a constant 128 factor of the reference current)

The internal reference is typically -1.20 V with a tolerance of  $\pm 0.05$  V and a typical drift of 50 ppm/°C. If greater accuracy or temperature stability is required, an external reference can be utilized.

## **OUTPUTS**

The output of the SPT9712 is comprised of complementary current sinks,  $I_{Out}$  and  $I_{\overline{Out}}$ . The output current levels at either  $I_{Out}$  or  $I_{\overline{Out}}$  are based upon the digital input code. The sum of the two is always equal to the full-scale output current minus one LSB.

By terminating the output current through a resistive load to ground, an associated voltage develops. The effective resistive load ( $R_{\text{Eff}}$ ) is the output resistance of the device ( $R_{\text{Out}}$ ) in parallel with the resistive load ( $R_{\text{L}}$ ). The voltage which develops can be determined using the following formulas:

```

Control Amp Out = -1.2 V, and R<sub>Set</sub> = 7.5 k\Omega I<sub>Out</sub> (FS) = (-1.2 V / 7.5 k\Omega) x 128 = -20.48 mA R<sub>L</sub> = 51 \Omega R<sub>Out</sub> = 1.0 k\Omega R<sub>Eff</sub> = 51 \Omega || 1.0 k\Omega = 48.52 \Omega V<sub>Out</sub> = R<sub>Eff</sub> x I<sub>Out</sub> (FS) = 48.52 \Omega x -20.48 mA = -0.994 V

```

The resistive load of the SPT9712 can be modified to incorporate a wide variety of signal levels. However, optimal device performance is achieved when the outputs are equivalently loaded.

**SPT9712**

4 2/15/01

Figure 1 - Timing Diagram

Figure 2 - Typical Interface Circuit

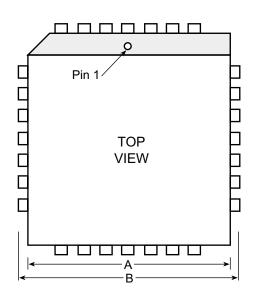

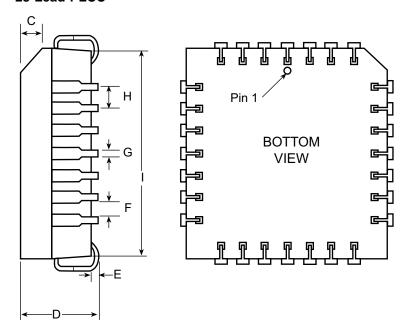

# PACKAGE OUTLINE

# 28-Lead PLCC

|        | INCH  | IES   | MILLIN | METERS |

|--------|-------|-------|--------|--------|

| SYMBOL | MIN   | MAX   | MIN    | MAX    |

| Α      | 0.452 | 0.456 | 11.48  | 11.58  |

| В      | 0.485 | 0.495 | 12.32  | 12.57  |

| С      | 30    | ٥     | 3      | 0°     |

| D      | 0.170 | 0.179 | 4.32   | 4.55   |

| E      | 0.020 | 0.025 | 0.51   | 0.64   |

| F      | 0.031 | 0.035 | 0.79   | 0.89   |

| G      | 0.013 | 0.021 | 0.33   | 0.53   |

| Н      | 0.048 | 0.052 | 1.22   | 1.32   |

| Ī      | 0.410 | 0.430 | 10.41  | 10.92  |

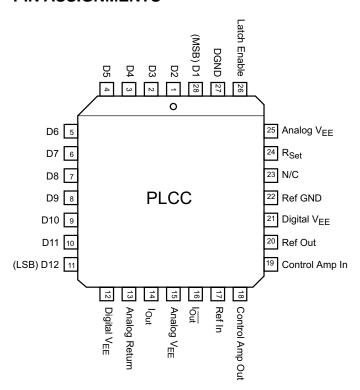

#### **PIN ASSIGNMENTS**

#### **PIN FUNCTIONS**

| Name                                                                                | Function                                                                                           |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Out+                                                                                | Analog Current Output                                                                              |

| Out-                                                                                | Complementary Analog Current Output                                                                |

| D1-D12                                                                              | Digital Input Bits (D12 is the LSB)                                                                |

| Latch Enable                                                                        | Latch Control Line                                                                                 |

| Ref In                                                                              | Voltage Reference Input                                                                            |

| Ref Out                                                                             | Internal Voltage Reference Output<br>Normally Connected to Control Amp In                          |

| Ref GND                                                                             | Ground Return For Internal Voltage<br>Reference and Amplifier                                      |

| Control Amp In Normally Connected to Ref Out If Not Connected to External Reference |                                                                                                    |

| Control Amp Out                                                                     | Output of Internal Control Amplifier<br>Normally Connected to Ref In                               |

| R <sub>Set</sub> 1                                                                  | Connection for External Resistance Reference When Using Internal Amplifier Nominally 7.5 $k\Omega$ |

| Analog Return                                                                       | Analog Return Ground                                                                               |

| Analog V <sub>EE</sub>                                                              | Analog Negative Supply (-5.2 V)                                                                    |

| Digital V <sub>EE</sub>                                                             | Digital Negative Supply (-5.2 V)                                                                   |

| DGND                                                                                | Digital Ground Return                                                                              |

| N/C                                                                                 | Not Connected                                                                                      |

<sup>1</sup>Full-Scale Current Out = 128 (Control Amp In / R<sub>Set</sub>)

#### ORDERING INFORMATION

| PART NUMBER | DNL/INL    | TEMPERATURE RANGE | PACKAGE  |

|-------------|------------|-------------------|----------|

| SPT9712AIP  | ±0.75/±1.0 | −40 to +85 °C     | 28L PLCC |

| SPT9712BIP  | ±1.25/±1.5 | −40 to +85 °C     | 28L PLCC |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

© Copyright 2002 Fairchild Semiconductor Corporation