# SPT5400

# 13-BIT, OCTAL VOLTAGE-OUTPUT DAC WITH PARALLEL INTERFACE

**APPLICATIONS**

• Flat-panel displays

Instrumentation

Process control

Automatic test equipment

Arbitrary function generators

# FEATURES

- Full 13-bit performance without external adjustments

- Eight DACs in one package

- · Buffered voltage outputs

- · Guaranteed monotonic to 13 bits

- Unipolar or bipolar output swing to ±4.5 V

- Output settling time of 7  $\mu$ s to ±1/2 LSB

- Double-buffered digital inputs

# DESCRIPTION

The SPT5400 has eight 13-bit voltage output digital-toanalog converters on one chip. It operates from  $\pm 5$  V power supplies and has maximum voltage output swings of up to  $\pm 4.5$  V without the addition of external components. Novel circuit topology allows for a guaranteed monotonicity of 13 bits without the need for additional circuitry. The SPT5400 has four separate reference voltage inputs, one for each pair of DACs. Four separate analog ground pins allow for separate offset voltages for each DAC pair. Each DAC can be asynchronously loaded through a common 13-bit bus into a double-buffered set of latches. All logic inputs are TTL/CMOS compatible.

The SPT5400 is available in a 44-lead PLCC package over the commercial temperature range of 0 °C to +70 °C.

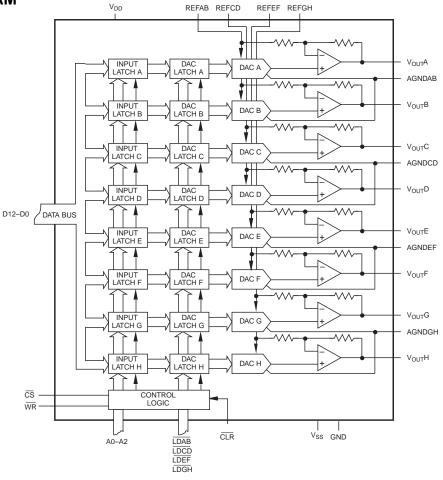

# **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)<sup>1</sup> 25 °C

#### **Supply Voltages**

| V <sub>DD</sub> to GND |                                                              |

|------------------------|--------------------------------------------------------------|

| V <sub>SS</sub> to GND |                                                              |

| AGNDxx                 | $(GND - 0.3 \text{ V}) \text{ to } (V_{DD} + 0.3 \text{ V})$ |

#### **Input Voltages**

| Digital Input Volt | tage to GND0.3 V to | $(V_{DD} + 0.3 V)$ |

|--------------------|---------------------|--------------------|

| REFxx              | (AGNDxx – 0.3 V) to | $(V_{DD} + 0.3 V)$ |

| Maximum Curre      | nt into REFxx Pin   | ±10 mA             |

#### Output

| V <sub>OUT</sub> xx | 1/ 10// |

|---------------------|---------|

| VOUTXX              |         |

| •001/00             |         |

#### Temperature

| Operating Temperature, Ambient0 to +70 °C        |

|--------------------------------------------------|

| Junction Temperature+165 °C                      |

| Lead Temperature, (soldering 10 seconds) +300 °C |

| Storage Temperature65 to +150 °C                 |

| Power Dissipation 1000 mW                        |

|                                                  |

Note 1: Operation at any Absolute Maximum Rating is not implied. Operation beyond the ratings may cause damage to the device. See Electrical Specifications for proper nominal applied conditions in typical applications.

# **ELECTRICAL SPECIFICATIONS**

$V_{DD}$  = +5 V,  $V_{SS}$  = -5 V, REFxx = 4.096 V, AGNDxx = GND = 0 V, R<sub>L</sub> = 10 k $\Omega$ , C<sub>L</sub> = 50 pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise specified. Typical values are at T<sub>A</sub> = +25 °C.

| PARAMETERS                                                                                                                                                                                     | TEST<br>CONDITIONS              | TEST<br>LEVEL                           | MIN          | SPT5400<br>TYP                                                          | МАХ                                   | UNITS                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|--------------|-------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|

| DC Performance<br>Resolution<br>Integral Linearity<br>Differential Linearity<br>Zero Code Error <sup>1</sup><br>Gain Error <sup>2</sup><br>Power Supply Rejection Ratio <sup>3</sup>           | Guaranteed Monotonic            |                                         | 13           | ±0.5<br>±10.0<br>±1.0                                                   | ±4.0<br>±1.0<br>±20<br>±15<br>±0.0025 | Bits<br>LSB<br>LSB<br>LSB<br>LSB<br>%/% |

| ∆Gain/∆V <sub>DD</sub><br>∆Gain/∆V <sub>SS</sub><br>Load Regulation                                                                                                                            | $R_L = \infty$ to 10 k $\Omega$ | VI<br>VI<br>V                           |              | ±0.4                                                                    | ±0.0025<br>±0.0025                    | %/%<br>%/%<br>LSB                       |

| Reference Input<br>Ref Input Range <sup>4,5</sup><br>Ref Input Resistance <sup>5</sup>                                                                                                         |                                 | IV<br>VI                                | AGND<br>5    |                                                                         | V <sub>DD</sub>                       | V<br>kΩ                                 |

| Analog Output<br>Maximum Output Voltage<br>Minimum Output Voltage<br>Output Slew Rate<br>Output Settling Time <sup>6</sup><br>Digital Feedthrough<br>Digital Crosstalk                         | To $\pm 1/2$ LSB of Full Scale  | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |              | V <sub>DD</sub> - 0.5<br>V <sub>SS</sub> + 0.5<br>2.4<br>7.0<br>5<br>50 |                                       | V<br>V<br>V/μs<br>μs<br>nV-s<br>nV-s    |

| Digital Inputs ( $V_{DD} = 5 V \pm 5\%$ )<br>Input Voltage High<br>Input Voltage Low<br>Input Current ( $V_{IN} = 0 V \text{ or } V_{DD}$ )<br>Input Capacitance                               |                                 | VI<br>VI<br>VI<br>IV                    | 2.4          |                                                                         | 0.8<br>10.0<br>10                     | V<br>V<br>μA<br>pF                      |

| Power Supplies<br>Positive Supply Range (V <sub>DD</sub> )<br>Negative Supply Range (V <sub>SS</sub> )<br>Positive Supply Current<br>Negative Supply Current<br>Power Dissipation <sup>7</sup> |                                 | VI<br>VI<br>VI<br>VI                    | 4.75<br>5.25 | 15<br>16<br>155                                                         | 5.25<br>4.75<br>25<br>25<br>250       | V<br>V<br>mA<br>mA<br>mW                |

<sup>1</sup>Deviation of actual DAC output when all 0s are loaded to the DAC from the ideal output of -4.096 V.

<sup>2</sup>Deviation of actual DAC output span from the ideal span of 8.191 V.

<sup>3</sup>PSSR is tested by changing the respective supply voltage by  $\pm$ 5%.

<sup>4</sup>For best performance, REF should be greater than AGND + 2 V and less than  $V_{DD}$  – 0.6 V. The device operates with reference inputs outside this range, but performance may degrade.

<sup>5</sup>Reference input resistance is code dependent.

$^{6}$ Typical settling time with 1000 pF capacitive load is 8  $\mu$ s.

<sup>7</sup>Does not include reference power.

#### **TEST LEVEL CODES**

#### TEST LEVEL TEST PROCEDURE

All electrical characteristics are subject to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data column indicates that the specification is not tested at the specified condition.

I

100% production tested at the specified temperature.

II

100% production tested at T<sub>A</sub> = +25 °C, and sample tested at the specified temperatures.

III

QA sample tested only at the specified temperatures.

IV

Parameter is guaranteed (but not tested) by design and characterization data.

V

Parameter is a typical value for information purposes only.

VI

100% production tested at T<sub>A</sub> = +25 °C. Parameter is guaranteed over

specified temperature range.

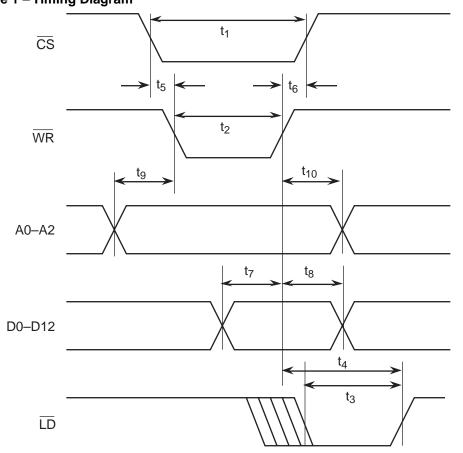

Figure 1 – Timing Diagram

#### NOTES:

1. All input rise and fall times are measured from 10% to 90% of +5 V.  $t_R = t_F = 5$  ns.

2. If LD is activated while WR is low, LD must stay low for t<sub>3</sub> or longer after WR goes high.

#### Table I – Timing Parameters

| PARAMETER                | SYMBOL            | MIN | TYP | MAX | UNIT |

|--------------------------|-------------------|-----|-----|-----|------|

| CS Pulse Width Low       | t <sub>1</sub>    | 50  |     |     | ns   |

| WR Pulse Width Low       | t <sub>2</sub>    | 50  |     |     | ns   |

| LD Pulse Width Low       | t <sub>3</sub>    | 50  |     |     | ns   |

| CLR Pulse Width Low      | t4                | 100 |     |     | ns   |

| CS to WR Low             | t <sub>5</sub>    | 0   |     |     | ns   |

| CS High to WR High       | t <sub>6</sub>    | 0   |     |     | ns   |

| Data Valid to WR Setup   | t <sub>7</sub>    | 20  |     |     | ns   |

| Data Valid to WR Hold    | t <sub>8</sub>    | 0   |     |     | ns   |

| Address Valid to WR Set  | up t <sub>9</sub> | 10  |     |     | ns   |

| Address Valid to WR Hold | d t <sub>10</sub> | 0   |     |     | ns   |

# **GENERAL CIRCUIT DESCRIPTION**

The SPT5400 contains eight 13-bit, voltage-output DACs. It uses a novel circuit topology to convert the 13-bit digital inputs into equivalent output voltages that are proportionate to the applied reference voltage. The SPT5400 has four separate reference voltage (REFxx) and analog ground (AGNDxx) inputs for each DAC pair. The REFxx inputs allow for separate full-scale output voltages for each DAC pair. The AGNDxx inputs allow for separate offset voltages for each DAC pair.

## VOLTAGE REFERENCE AND ANALOG GROUND INPUTS

The REFxx and AGNDxx inputs set the output range of the corresponding DAC pair. For a detailed description of the relationship between the DAC output range and the REFxx and AGNDxx input voltages, see the Analog Outputs section of this datasheet.

The reference input impedance is code dependent. It is at its highest value when the input code of the corresponding DAC pair is all 1s. It is at its lowest value when the input code is all 0s. Because the input impedance is code dependent, load regulation of the reference is critical.

# **MULTIPLYING OPERATION**

Because the reference of the SPT5400 accepts both AC and DC signals, it can be used for multiplying applications. The REFxx inputs (which set the full-scale output voltage for the respective DACs) only accept positive voltages, so the multiplying operation is limited to two quadrants. Note that when applying AC signals to the reference, do not bypass the inputs.

## DIGITAL INPUTS AND MICROPROCESSOR INTERFACE

All digital inputs are TTL/CMOS compatible. The SPT5400 is compatible with microprocessors having a minimum 13-bit-wide data bus. The microprocessor interface is double-buffered to allow all the DACs to be simultaneously updated.

# DAC ADDRESSING AND LATCHING

Each DAC has an input latch that receives data from the data bus, and a DAC latch that receives data from the input latch. The address lines (A0–A2) for each DAC input latch are shown in table II. Data is transferred from the input latch to the DAC latch when LDxx is asserted. The analog output of each DAC reflects the data held in its corresponding DAC latch. In addition to being latched, data can be transferred to the DAC directly through transparent latches.

## Table II – DAC Addressing

| A2 | A1 | A0 | Function          |

|----|----|----|-------------------|

| 0  | 0  | 0  | DAC A input latch |

| 0  | 0  | 1  | DAC B input latch |

| 0  | 1  | 0  | DAC C input latch |

| 0  | 1  | 1  | DAC D input latch |

| 1  | 0  | 0  | DAC E input latch |

| 1  | 0  | 1  | DAC F input latch |

| 1  | 1  | 0  | DAC G input latch |

| 1  | 1  | 1  | DAC H input latch |

The control inputs of the SPT5400 are level triggered, and are shown in table III. The input latch is controlled by  $\overline{CS}$  and  $\overline{WR}$ , and the transfer of data to the DAC latch is controlled by  $\overline{LDxx}$ . When  $\overline{CS}$  and  $\overline{WR}$  are low, the input latch is transparent. When  $\overline{LDxx}$  is low the DAC latch is transparent. To avoid transferring data to the wrong DAC, the address lines (A0–A2) must be valid through the time  $\overline{CS}$  and  $\overline{WR}$  are low. See the timing diagram for specific timing values. When  $\overline{CS}$  and  $\overline{WR}$  are high, the data is latched into the input latch. When  $\overline{LDxx}$  is low when  $\overline{CS}$  and  $\overline{WR}$ are low, then it must be held low for t<sub>3</sub> or longer after  $\overline{CS}$  or  $\overline{WR}$  goes high.

When  $\overline{\text{CLR}}$  is low, all DAC outputs are set to their corresponding AGNDxx. When  $\overline{\text{CLR}}$  toggles from low to high, 1000hex is latched into all input and DAC latches.

#### Table III – Interface Truth Table

| CLR | LDXX | WR | CS | Function                                                |

|-----|------|----|----|---------------------------------------------------------|

| 1   | 0    | 0  | 0  | Both latches transparent                                |

| 1   | 1    | 1  | Х  | Both latches latched                                    |

| 1   | 1    | х  | 1  | Both latches latched                                    |

| 1   | х    | 0  | 0  | Input latch transparent                                 |

| 1   | х    | 1  | Х  | Input latch latched                                     |

| 1   | Х    | х  | 1  | Input latch latched                                     |

| 1   | 0    | х  | Х  | DAC latch transparent                                   |

| 0   | х    | х  | х  | All input and DAC latches at 1000hex, outputs at AGNDxx |

# **DIGITAL CODE**

The SPT5400 uses offset binary coding. Conversion to a 13-bit offset binary code from a 13-bit twos-complement code can be achieved by adding  $2^{12} = 4096$ .

## POWER SUPPLY SEQUENCING

The required power-up sequence is as follows:  $V_{SS}$  (or  $V_{DD}$ ) first,  $V_{DD}$  (or  $V_{SS}$ ) second, and then REF\_. The sequence in which  $V_{DD}$  and  $V_{SS}$  come up is not critical. However, REF\_ must come up after  $V_{DD}$  and  $V_{SS}$  are established.

Fairchild strongly recommends that the digital input pins be driven only after  $V_{DD}$  and  $V_{SS}$  are established. Driving a digital input prior to establishing supplies will violate a condition outlined in the Input Voltages section (see the Absolute Maximum Ratings on page 2 of this data sheet) and cause damage to the part. If either REF\_ or the digital inputs must come up before  $V_{DD}$  and  $V_{SS}$ , due to system constraints, limit the current to the REF\_ or digital input pins to less than 1 mA.

This recommended power-up sequence must be executed in reversed order for power-down. It should be noted that none of the Absolute Maximum Rating conditions are violated during power-up and power-down.

# ANALOG OUTPUTS

The voltage outputs to the SPT5400 are buffered internally by precision amplifiers with a 2.4 V/µs typical slew rate. The typical settling time to  $\pm 1/2$  LSB, with a full-scale transition at the outputs, is 7 µs. Each DAC output is protected against a short to GND or AGNDxx. The typical short-circuit currents are 25 mA when the DAC is at positive full scale, and 2.5 mA when the DAC is at negative full scale.

#### BIPOLAR OUTPUT VOLTAGE RANGE (AGNDxx = 0 V)

For symmetrical bipolar operation, AGNDxx should be tied to the system ground. The relationship between the output voltage and the digital code is shown in table IV. The output voltage of the DAC ladder (VDAC) is multiplied by 2 and level-shifted by the reference voltage. The output voltage of the amplifier is given by the following equation:

$$V_{OUT} = 2(VDAC) - REFxx$$

Where VDAC is the voltage at the noninverting input of the amplifier and REFxx is the voltage at the reference input of the DAC.

With AGNDxx connected to the system ground, the output voltage of the DAC ladder is:

$$VDAC = (D/2^{13})REFxx$$

Where D is the numeric value of the DAC's binary input code.

Replacing VDAC in the equation gives the output voltage.

$$V_{OUT}xx=2\left(\frac{D}{2^{13}}\right)(REFxx) - REFxx = REFxx\left(\frac{D}{2^{12}} - 1\right) = REFxx\left(\frac{D}{4096} - 1\right)$$

$$1 LSB = REFxx\left(\frac{1}{4096}\right)$$

D ranges from 0 to 8191 (2<sup>13</sup>-1).

#### Table IV – Input Code/Output Tables

#### Bipolar (AGNDxx = 0 V)

| Input            | Output             |

|------------------|--------------------|

| 1 1111 1111 1111 | +REFxx (4095/4096) |

| 1 0000 0000 0001 | +REFxx (1/4096)    |

| 1 0000 0000 0000 | 0 V                |

| 0 1111 1111 1111 | –REFxx (1/4096)    |

| 0 0000 0000 0001 | –REFxx (4095/4096) |

| 0 0000 0000 0000 | –REFxx             |

#### Positive Unipolar (AGNDxx = REFxx/2)

|                  | ,                  |

|------------------|--------------------|

| Input            | Output             |

| 1 1111 1111 1111 | +REFxx (8191/8192) |

| 1 0000 0000 0000 | +REFxx/2           |

| 0 0000 0000 0000 | 0 V                |

|                  |                    |

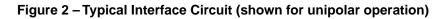

#### POSITIVE UNIPOLAR OUTPUT VOLTAGE RANGE (AGNDxx = REFxx/2)

For positive unipolar operation, AGNDxx should be set to REFxx/2. The relationship between the output voltage and the digital code is shown in table IV. For example, if a 4.096 V reference is used, AGNDxx should be offset by 2.048 V. This results in a unipolar output voltage of 0 to 4.0955 V, where 1 LSB = 500  $\mu$ V. the maximum current out of any AGNDxx pin is:

$$I_{AGNDXX} = \left(\frac{\text{REFxx} - \text{AGNDxx}}{5 \text{ k}\Omega}\right)$$

#### CUSTOM OUTPUT VOLTAGE RANGE

If the voltage at the REFxx input is higher than the voltage at the AGNDxx input, the AGNDxx inputs can be offset by any voltage within the supply rails. One way to achieve this is to add positive offset to AGNDxx by selecting the reference voltage and the voltage at AGNDxx such that the resulting output voltages do not come within  $\pm 0.5$  V of the supply rails. Another way is to digitally offset AGNDxx by connecting one DAC output to one or more AGNDxx inputs. Note that a DAC output should not be connected to its own AGNDxx input.

The relationship between the reference, AGNDxx and output voltage is shown in table V.

#### Table V – Relationship between Reference, AGNDxx and Output

| PARAMETER                                                           | BIPOLAR OPERATION<br>(AGNDxx = 0 V) | POSITIVE<br>UNIPOLAR OPERATION<br>(AGND = REFxx/2) | CUSTOM OPERATION           |

|---------------------------------------------------------------------|-------------------------------------|----------------------------------------------------|----------------------------|

| Bipolar Zero Level or Unipolar Mid-Scale<br>(Code = 100000000000)   | AGNDxx = 0 V                        | AGNDxx = REFxx/2                                   | AGNDxx                     |

| Differential Reference Voltage (VDR)                                | REFxx                               | REFxx/2                                            | REF – AGNDxx               |

| Negative Full-Scale Output (Code = All 0s)                          | ) –REFxx                            | 0 V                                                | AGNDxx – VDR               |

| Positive Full-Scale Output (Code = All 1s)                          | (4095/4096)(REFxx)                  | (8191/8192)(REFxx)                                 | AGNDxx + (4095/4096)(VDR)  |

| LSB Weight                                                          | (REFxx/4096)                        | (REFxx/8192)                                       | (VDR/4096)                 |

| V <sub>OUT</sub> xx as a Function of Digital Code<br>(D, 0 to 8191) | ((D/4096)-1)(REFxx)                 | (D/8192)(REFxx)                                    | AGNDxx + ((D/4096)-1)(VDR) |

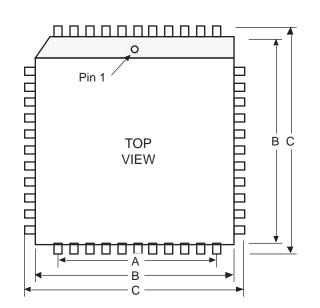

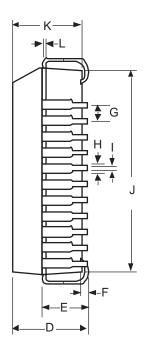

# PACKAGE OUTLINE

## 44L PLCC

|        | INC   | INCHES   |       | METERS |

|--------|-------|----------|-------|--------|

| SYMBOL | MIN   | MAX      | MIN   | MAX    |

| А      | 0.5   | typ      | 12.7  | 0 typ  |

| В      | 0.650 | 0.655    | 16.51 | 16.64  |

| С      | 0.685 | 0.695    | 17.40 | 17.65  |

| D      | 0.165 | 0.180    | 4.19  | 4.57   |

| Е      | 0.100 | 0.110    | 2.54  | 2.79   |

| F      | 0.020 |          | 0.51  |        |

| G      | 0.05  | 0.05 typ |       | ′ typ  |

| Н      | 0.026 | 0.032    | 0.66  | 0.81   |

| I      | 0.013 | 0.021    | 0.33  | 0.53   |

| J      | 0.590 | 0.630    | 14.99 | 16.00  |

| K      | 0.145 | 0.156    | 3.68  | 3.96   |

| L      | 0.009 | 0.011    | 0.23  | 0.28   |

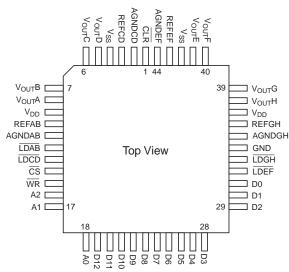

## **PIN ASSIGNMENTS**

## **PIN FUNCTIONS**

| Name               | Function                                                                                                                                                     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR                | Clear input (active low). Driving this asynchronous input low sets the content of all latches to 1000hex. All DAC outputs are reset to AGNDxx.               |

| AGNDCD             | Analog ground for DAC C and DAC D.                                                                                                                           |

| REFCD              | Reference voltage input for DAC C and DAC C. Bypass to AGNDCD with a 0.1 to 1 $\mu F$ capacitor.                                                             |

| V <sub>SS</sub>    | Negative power supply, $-5$ V (two pins). Connect both pins to the supply voltage. Bypass each pin to the system analog ground with a 0.1 $\mu$ F capacitor. |

| V <sub>OUT</sub> D | DAC D output voltage.                                                                                                                                        |

| V <sub>OUT</sub> C | DAC C output voltage.                                                                                                                                        |

| V <sub>OUT</sub> B | DAC B output voltage.                                                                                                                                        |

| V <sub>OUT</sub> A | DAC A output voltage.                                                                                                                                        |

| Name               | Function                                                                                                                                              |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DD</sub>    | Positive power supply, +5 V (two pins). Connect both pins to the supply voltage. Bypass each pin to the system analog ground with a 0.1 µF capacitor. |  |

| REFAB              | Reference voltage input for DAC A and DAC B Bypass to AGNDAB with a 0.1 to 1 $\mu$ F capacitor.                                                       |  |

| AGNDAB             | Analog ground for DAC A and DAC B.                                                                                                                    |  |

| LDAB               | Load input (active low). Driving this asynchronous input low transfers the contents of the input latches A and B to the respective DAC latches.       |  |

| LDCD               | Load input (active low). Driving this asynchronous input low transfers the contents of the input latches C and D to the respective DAC latches.       |  |

| CS                 | Chip select (active low).                                                                                                                             |  |

| WR                 | Write input (active low). $\overline{WR}$ along with $\overline{CS}$ load data into the DAC input latch selected by A0–A2.                            |  |

| A2                 | Address bit 2.                                                                                                                                        |  |

| A1                 | Address bit 1.                                                                                                                                        |  |

| A0                 | Address bit 0.                                                                                                                                        |  |

| D12–D0             | Data bits 12–0. (D0 = LSB)                                                                                                                            |  |

| LDEF               | Load input (active low). Driving this asynchronous input low transfers the contents of the input latches E and F to the respective DAC latches.       |  |

| LDGH               | Load input (active low). Driving this asynchronous input low transfers the contents of the input latches G and H to the respective DAC latches.       |  |

| GND                | Digital ground.                                                                                                                                       |  |

| AGNDGH             | Analog ground for DAC G and DAC H.                                                                                                                    |  |

| REFGH              | Reference voltage input for DAC G and DAC H.<br>Bypass to AGNDGH with a 0.1 to 1 $\mu$ F capacitor.                                                   |  |

| V <sub>OUT</sub> H | DAC H output voltage.                                                                                                                                 |  |

| V <sub>OUT</sub> G | DAC G output voltage.                                                                                                                                 |  |

| V <sub>OUT</sub> F | DAC F output voltage.                                                                                                                                 |  |

| V <sub>OUT</sub> E | DAC E output voltage.                                                                                                                                 |  |

| REFEF              | Reference voltage input for DAC E and DAC F. Bypass to AGNDEF with a 0.1 to 1 $\mu$ F capacitor.                                                      |  |

| AGNDEF             | Analog ground for DAC E and DAC F.                                                                                                                    |  |

|                    |                                                                                                                                                       |  |

# **ORDERING INFORMATION**

| PART NUMBER | TEMPERATURE RANGE | PACKAGE  |

|-------------|-------------------|----------|

| SPT5400SCP  | 0 to +70 °C       | 44L PLCC |

## DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

© Copyright 2002 Fairchild Semiconductor Corporation